#### [54] MINIATURE ELECTRONIC CALCULATOR

[75] Inventors: Jack S. Kilby; Jerry D. Merryman; James H. Van Tassel, all of Dallas,

Tex.

[73] Assignee: Texas Instruments Incorporated,

Dallas, Tex.

[22] Filed: Dec. 21, 1972

[21] Appl. No.: 317,493

## Related U.S. Application Data

[63] Continuation of Ser. No. 143,192, May 13, 1971, abandoned, which is a continuation of Ser. No. 671,777, Sept. 29, 1967, abandoned.

| [52] | U.S. Cl         | <b>235/156,</b> 235 | /159 |

|------|-----------------|---------------------|------|

| [51] | Int. Cl         | G06f                | 7/38 |

|      | Field of Search |                     |      |

| Ť.,  | . 34            | 10/365 347 DD: 219  | /201 |

| [56]      | R       | eferences Cited |            |

|-----------|---------|-----------------|------------|

|           | UNITED  | STATES PATEN    | TS         |

| 2,932,816 | 4/1960  | Stiefel et al   | 340/347 DD |

| 3,140,031 | 7/1964  | Fitch           | 226/109    |

| 3,315,069 | 4/1967  | Bohm            | 235/156 X  |

| 3,331,954 | 7/1967  | Kinzie et al    | 235/156    |

| 3,354,817 | 11/1967 | Sakurai et al   |            |

| 3,405,392 | 10/1968 | Milne et al     | 235/156 X  |

| 3,430,226 | 2/1969  | Chow            | 340/347    |

| 3,509,329 | 4/1970  | Wang et al      | 235/156    |

| 3,548,179 | 12/1970 | Kimura et al    | 235/156    |

| 3,553,445 | 1/1971  | Hernandez       | 235/156    |

## OTHER PUBLICATIONS

National Technical Report, Vol. 12, No. 2, 1966, pp. 129–137, (Published by Matsushita Electric Industrial

Co., Ltd., Japan).

Primary Examiner—Charles E. Atkinson

Assistant Examiner—James F. Gottman

Attorney, Agent, or Firm—Harold Levine; Edward

Connors, Jr.; John G. Graham

#### [57] ABSTRACT

Binary-coded decimal electronic calculator capable of adding, subtracting, multiplying and dividing with some degree of automatic decimal point placement to provide a visual display of answers of up to 12 decimal digits. The decimal digits are serially displayed at a speed compatible with the calculator operations. The parts of the calculator are so adapted electrically and mechanically in relation to each other to result in a minature portable battery operated calculator of extremely small dimensions for example the outside case dimensions of 414 inches by 61% inches by 134 inches and very low weight of about 45 ounces, having a calculating capability only before obtainable in calculators of much larger size and weight while retaining mechanical and operational simplicity. Some significant aspects of the calculator are the primary electronics embodied in an integrated semiconductor circuit array located in substantially one plane for performing the arithmetic calculations and generating the control signals, a keyboard input arrangement located in substantially one plane parallel to the integrated semiconductor circuit array for producing unique electrical signals corresponding to number and command entries and a visual display using a semiconductor array, as for a thermal printer for printout.

## 59 Claims, 36 Drawing Figures

SHEET 01 OF 21

SHEET 02 OF 21

SHEET 03 OF 21

Fig. 5

SHEET 04 OF 21

SHEET 05 OF 21

SHEET OS OF 21

SHEET 07 OF 21

SHEET 08 OF 21

SHEET 09 OF 21

SHEET 10 OF 21

SHEET 11 OF 22

SHEET 12 OF 21

SHEET 13 OF 21

SHEET 14 OF 21

SHEET 16 OF 21

SHEET 17 OF 21

SHEET 18 OF 21

SHEET 19 OF 21

# SHEET 20 OF 21

|                                  |    | Fig. 34 |

|----------------------------------|----|---------|

| KBN CL STP SAP                   |    |         |

| SS,RO<br>KCCP<br>CPI, <u>CP3</u> |    |         |

| 000                              | ππ |         |

SHEET 21 OF 21

## MINIATURE ELECTRONIC CALCULATOR

This application is a conitnuation of copending application Ser. No. 143,192, filed May 13, 1971 (now abandoned), which was a continuation of then- 5 copending application Ser. No. 671,777, filed Sept. 29, 1967 (now abandoned).

The present invention relates to electronic calculators and more particularly to miniature portable electronic calculators capable of adding, subtracting, multi-10 plying and dividing.

An object of the present invention is to provide an electronic calculator of a size substantially smaller than heretofore obtainable.

Another object of the present invention is to provide 15 grated semiconductor circuit array of FIG. 14; a miniature portable electronic calculator having a high degree of calculating capability and mechanical and operational simplicity.

A feature of the invention is a miniature electronic calculator having its primary electronics embodied in an integrated semiconductor circuit array located in substantially one plane for performing the arithmetic calculations and generating the control signals.

Another feature of the invention is a miniature electronic calculator having a keyboard encoder located in substantially one plane for encoding a mechanical entry into a unique signal and an integrated semiconductor circuit array located substantially in one plane parallel to the keyboard encoder for performing the 30 arithmetic calculations and generating the control signals.

Still another feature of the invention is a miniature electronic calculator having an integrated semiconductor circuit array located in substantially one plane for 35 performing the arithmetic calculations and generating the control signals for a thermal printer comprising an integrated semiconductor heater element array.

Other objects, features and advantages of the invention may be best understood by reference to the follow- 40 ing detailed description taken in conjunction with the accompanying drawings in which like reference numberals indicate like parts and in which:

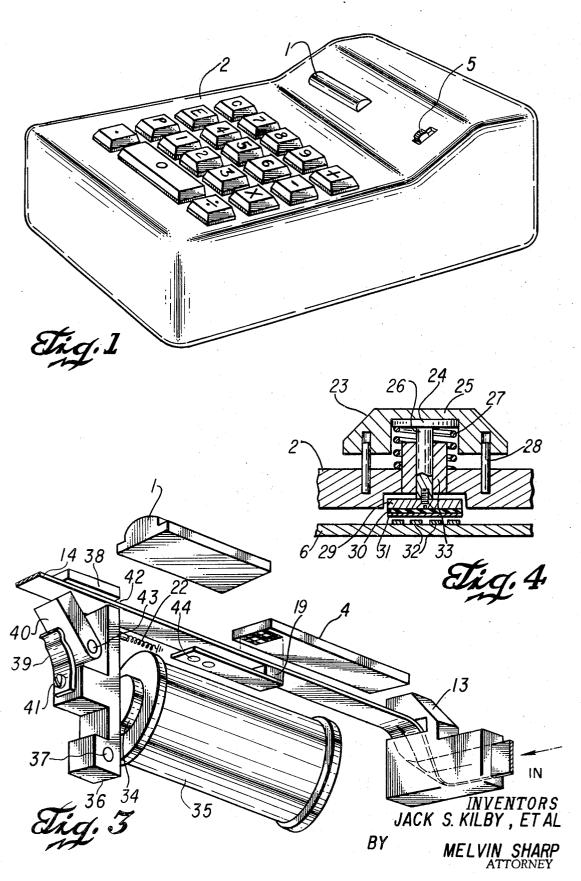

FIG. 1 illustrates the exterior casing of the calculator, according to an embodiment of the present invention; 45

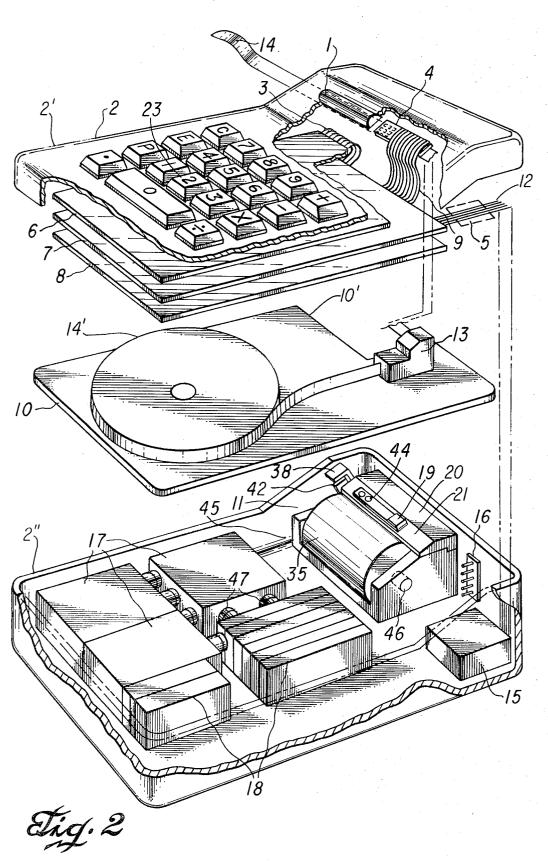

FIG. 2 illustrates the mechanical relationship of the parts of the calculator of FIG. 1;

FIG. 3 illustrates the tape advance system 11 and thermal printer 4 for printout in the calculator of FIG. 50

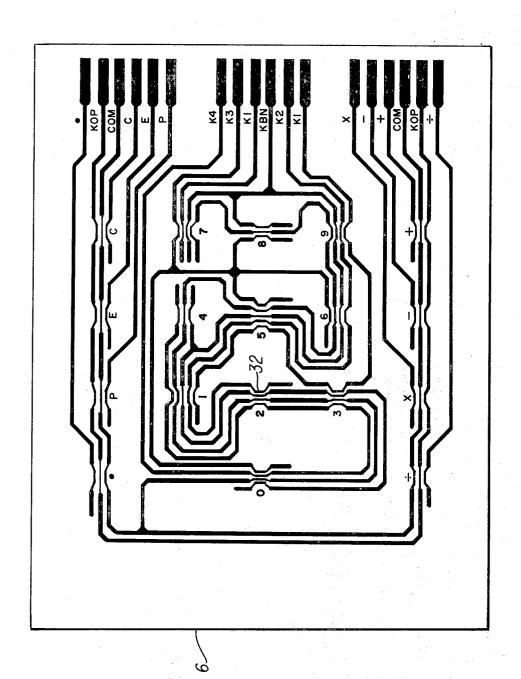

FIG. 4 illustrates the key 23 and keyboard encoder 6 of the calculator of FIG. 2;

FIG. 5 illustrates the keyboard encoder 6 of the calculator of FIG. 2;

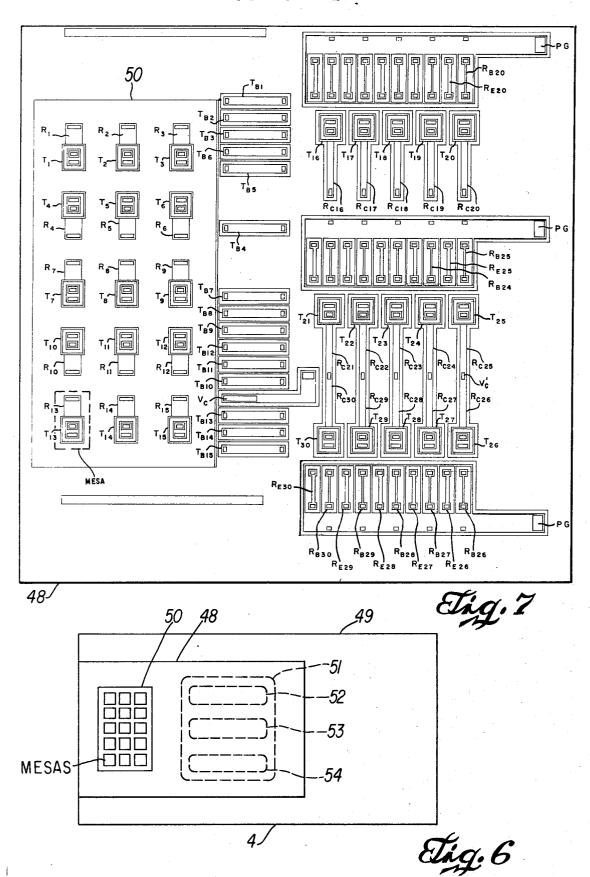

FIG. 6 illustrates the thermal printer 4 of the calculator of FIG. 2;

FIG. 7 illustrates the heater element array and drive matrix therefor of the thermal printer of FIG. 6;

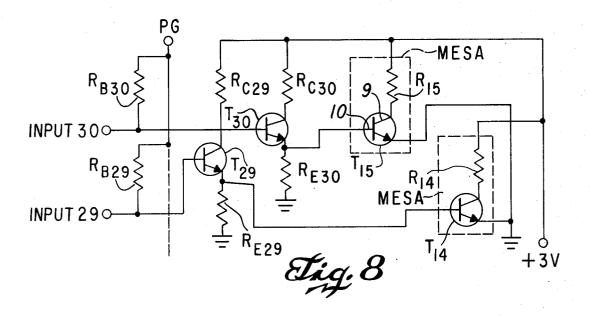

FIG. 8 illustrates the electrical schematic of the 60 heater element array and drive matrix therefor of the thermal printer of FIG. 6;

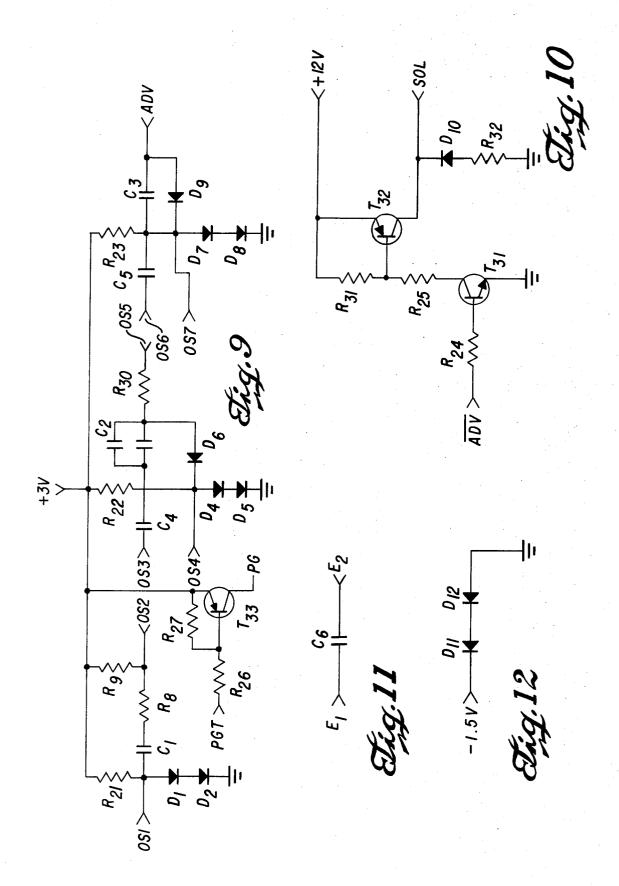

FIGS. 9-13 illustrate the power supply and auxiliary electronics of the calculator of FIG. 2;

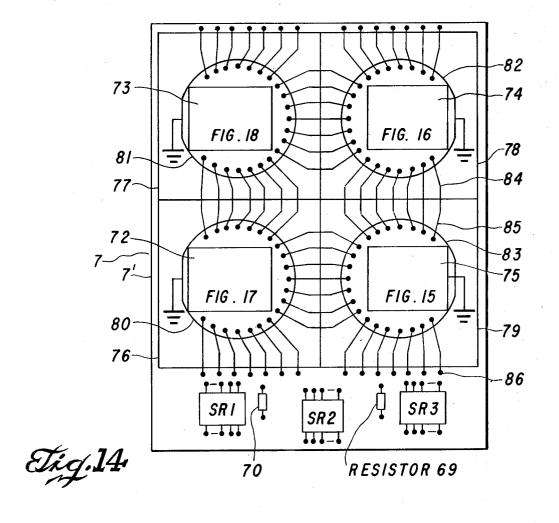

FIG. 14 illustrates the integrated semiconductor circuit array comprising the primary electronics 7 of the calculator of FIG. 2;

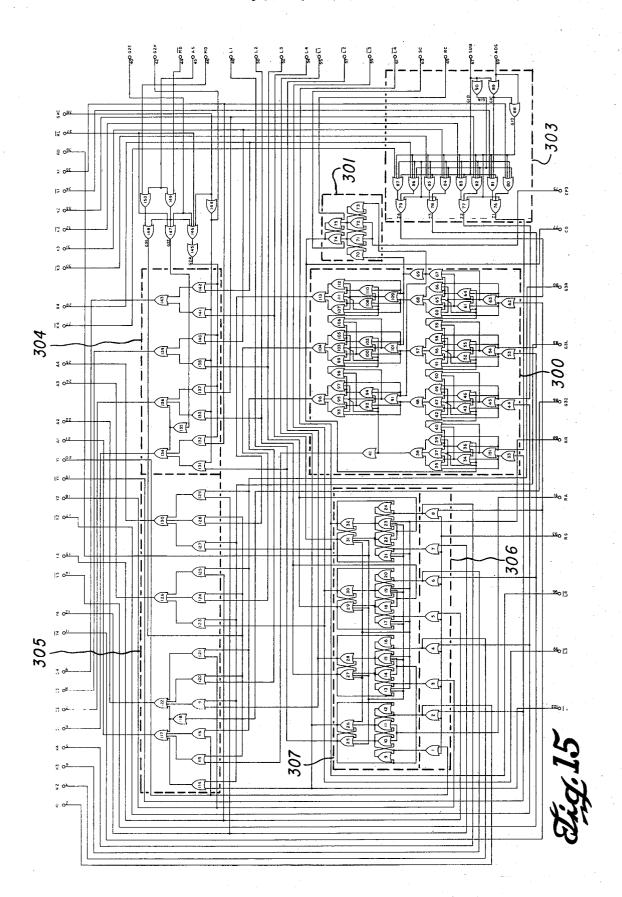

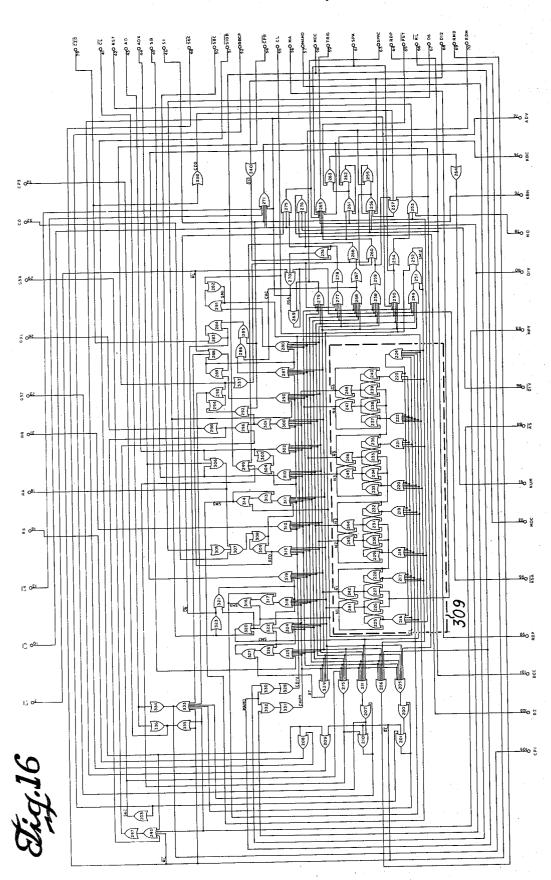

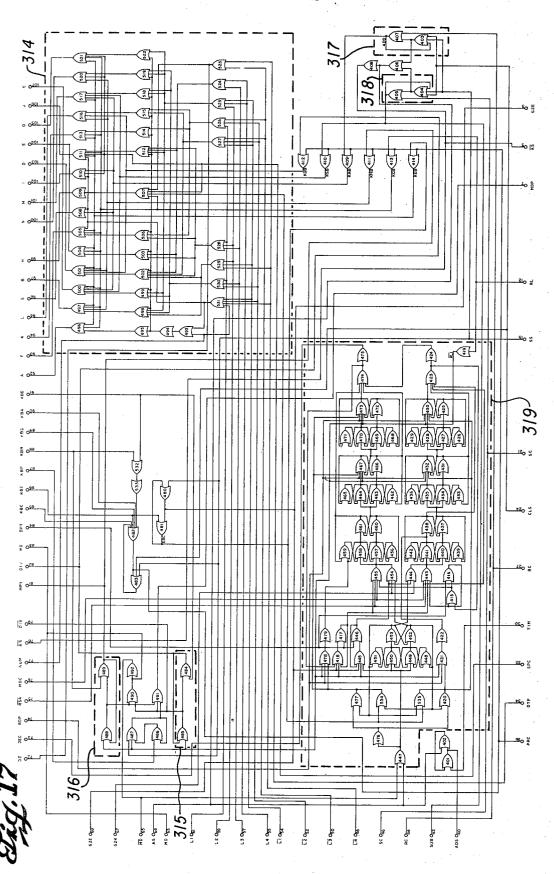

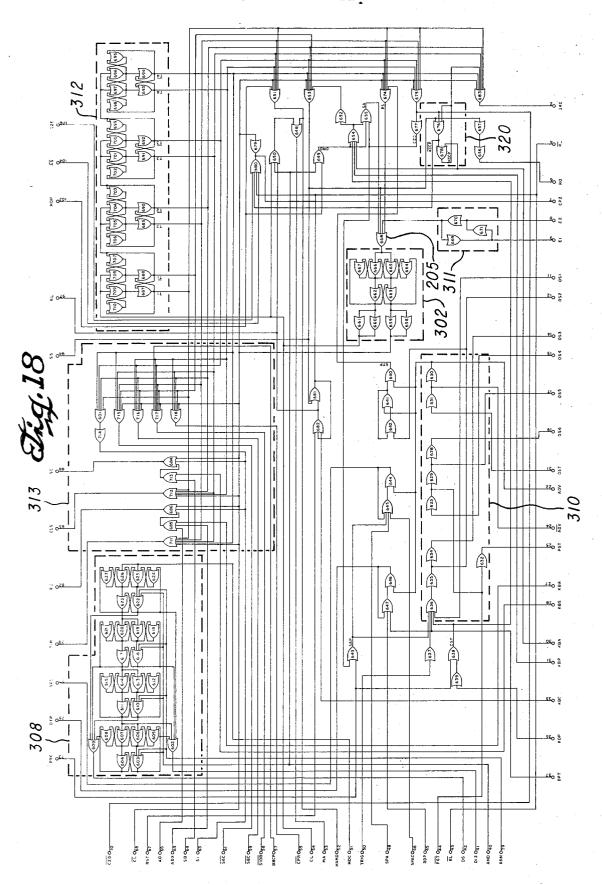

FIGS. 15-18 illustrate the logic circuitry of the integrated semiconductor circuit array of FIG. 14;

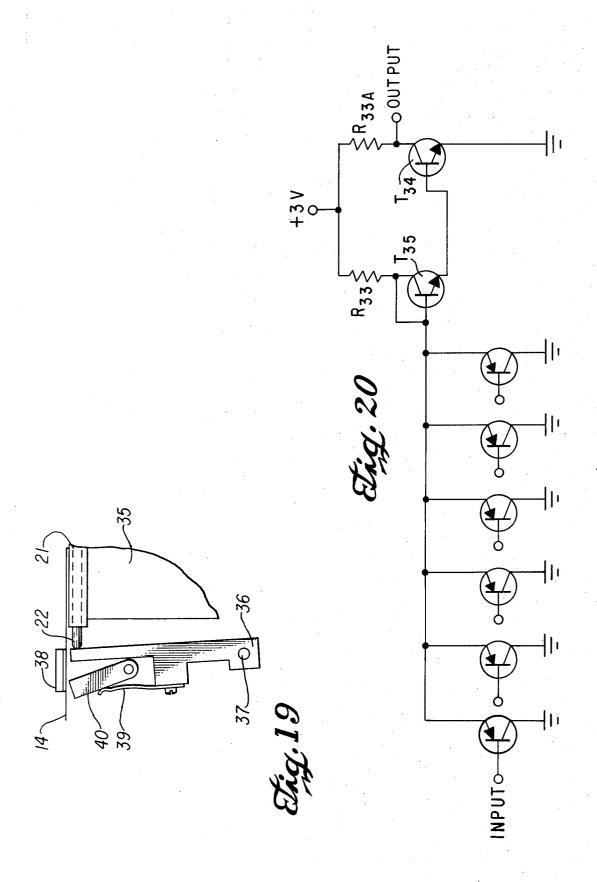

FIG. 19 illustrates a partial view of the tape advance system 11 of FIG. 2;

FIG. 20 illustrates a typical circuit comprising a gate in FIGS. 15-18;

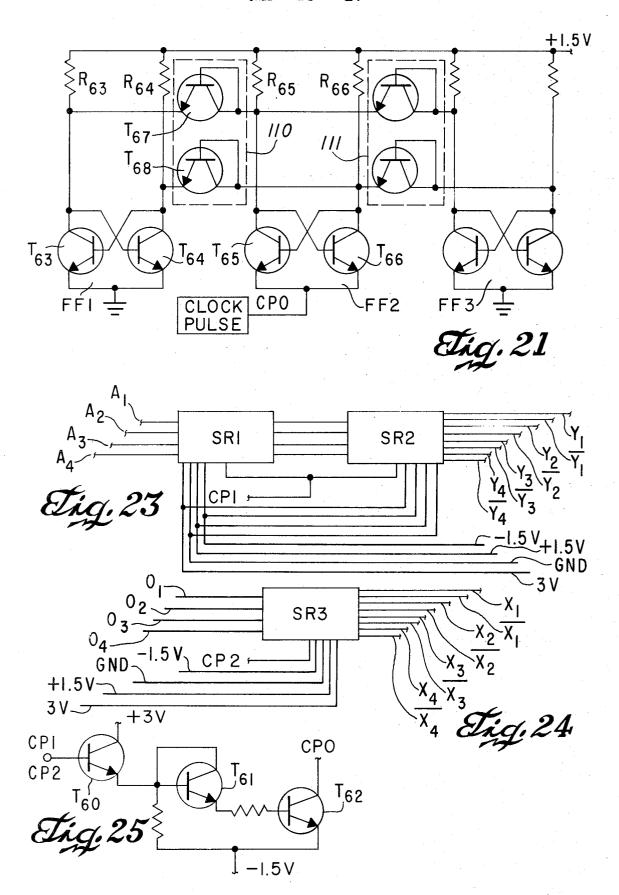

FIG. 21 illustrates a shift register circuit of the integrated semiconductor circuit array of FIG. 14;

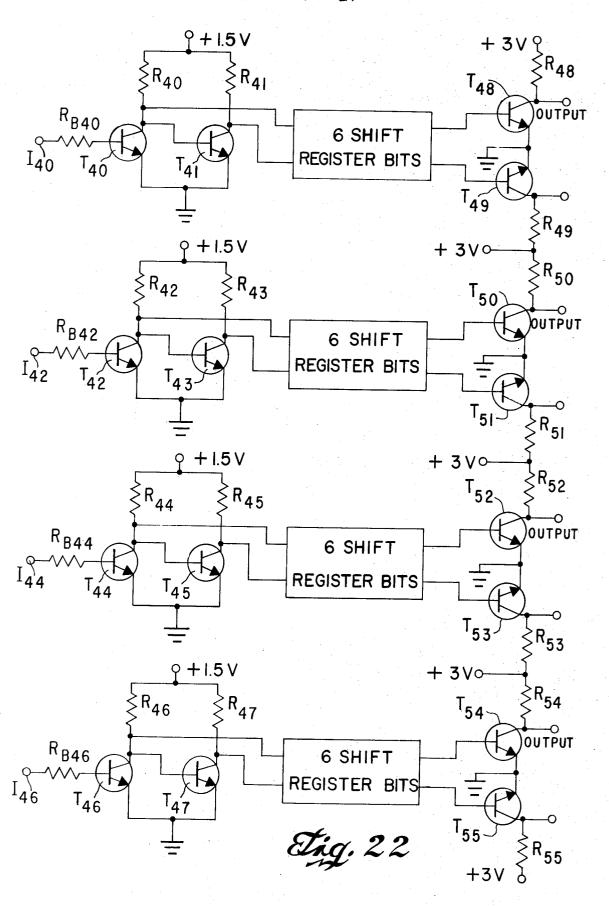

FIG. 22 illustrates a 24 bit shift register of the integrated semiconductor circuit array of FIG. 14;

FIG. 23 illustrates the interconnection of two 24 bit shift registers of the integrated semiconductor circuit array of FIG. 14;

FIG. 24 illustrates one 24 bit shift register of the inte-

FIG. 25 illustrates the clock pulse circuit of a shift register of the integrated semiconductor circuit array

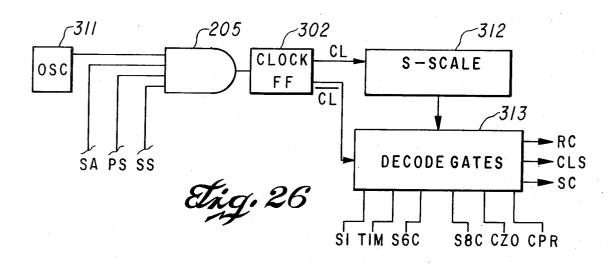

FIG. 26 illustrates a block diagram of a control section of the integrated semiconductor circuit array of FIG. 14;

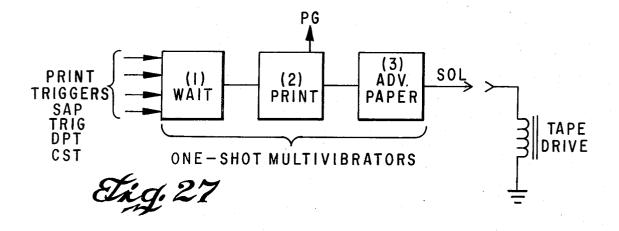

FIG. 27 illustrates a block diagram of the print control section of the integrated semiconductor circuit array of FIG. 14;

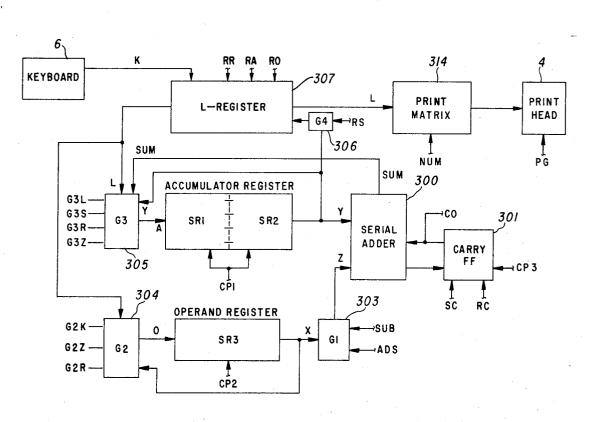

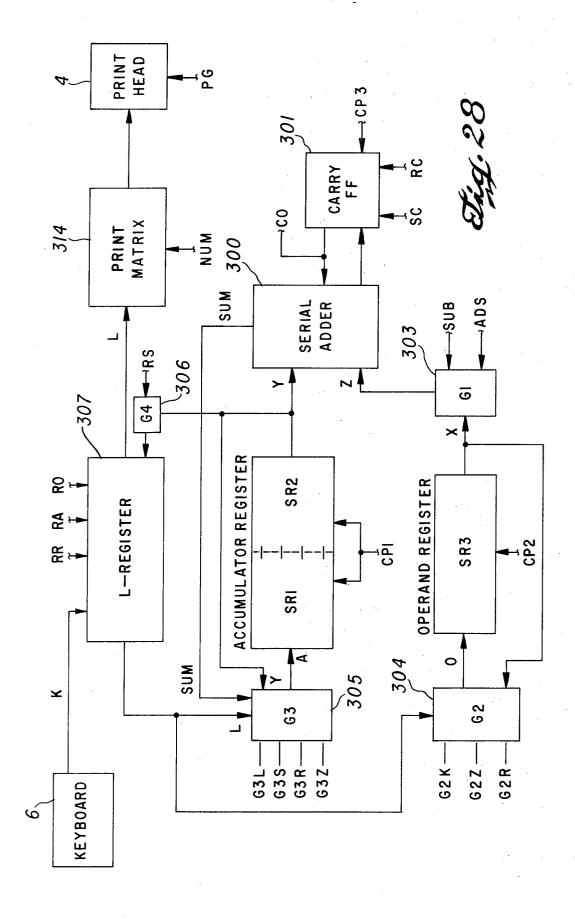

FIG. 28 illustrates a block diagram of the arithmetic section of the integrated semiconductor circuit array of FIG. 14;

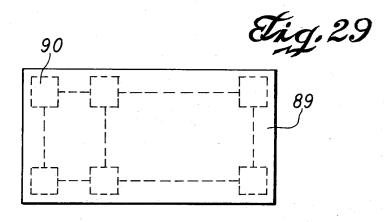

FIG. 29 illustrates an integrated semiconductor circuit embodying the logic circuits of FIGS. 15-18;

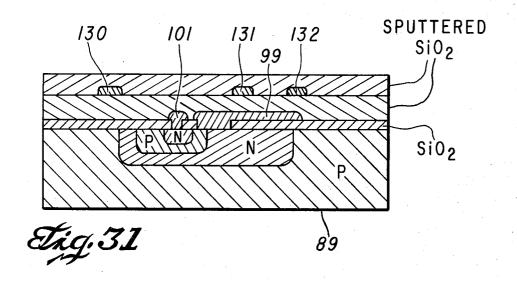

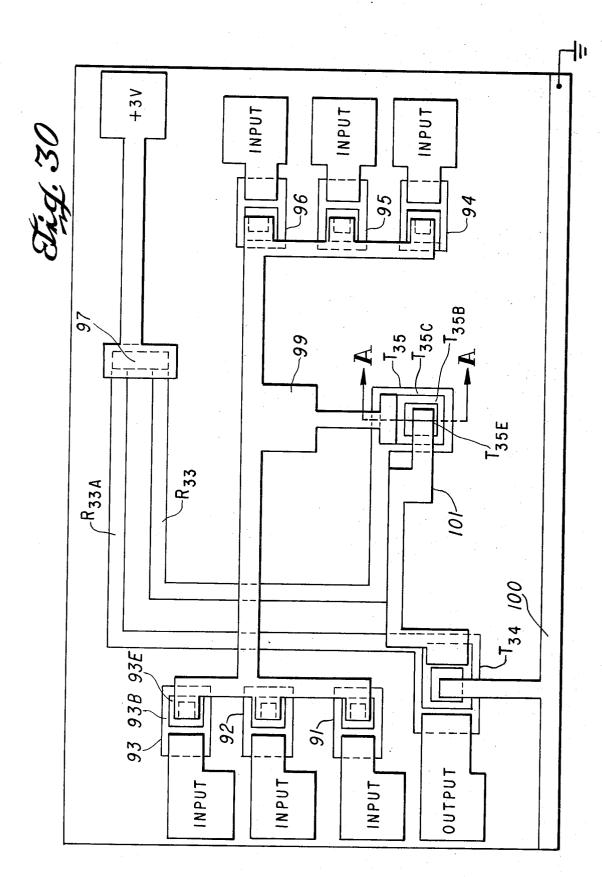

FIG. 30 illustrates the gate 90 of FIG. 29;

FIG. 31 illustrates a cross section of FIG. 30 taken along the lines A—A;

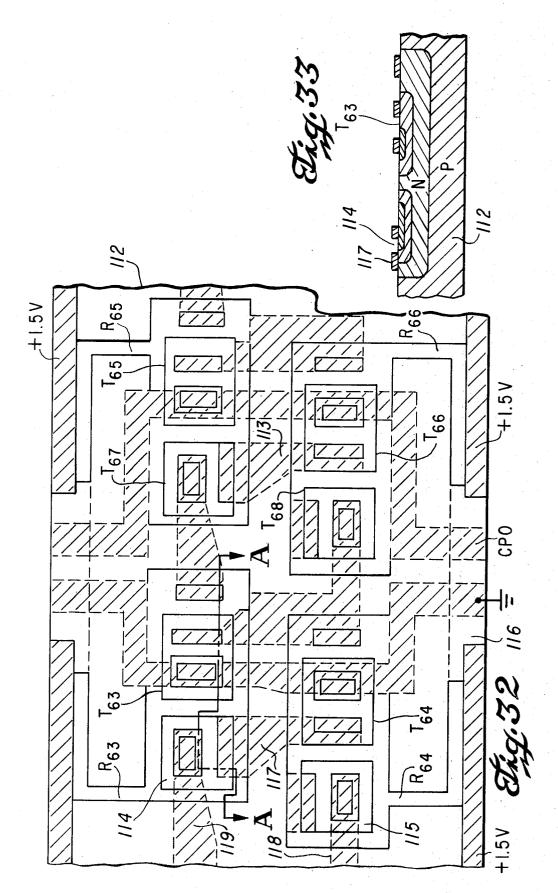

FIG. 32 illustrates an integrated semiconductor shift register of the integrated semiconductor circuit array of FIG. 14;

FIG. 33 illustrates a cross section of FIG. 32 taken along the line A—A in FIG. 32;

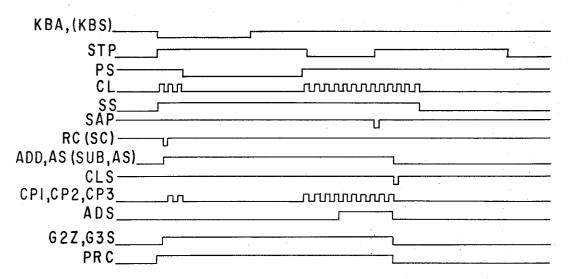

FIGS. 34 and 35 illustrate the timing diagrams of the commands for digit entry, add and subtract operations of the calculator of FIG. 2; and

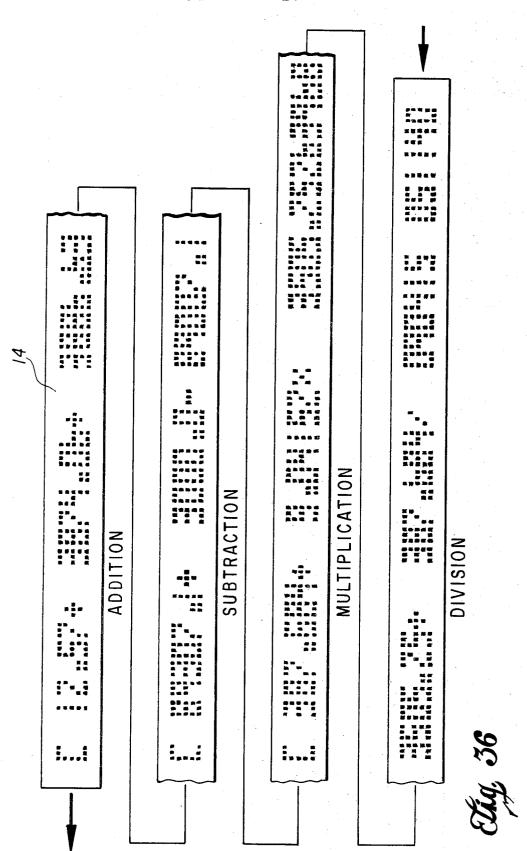

FIG. 36 illustrates the printout tape format.

Referring to FIG. 1, there is illustrated the exterior casing 2 of the miniature portable calculator according to an embodiment of the present invention in which the numeric and command entries are made to the calculator by depressing the numeric keys 0-9, the add key +, the subtract key -, the multiply key  $\times$ , the divide key  $\div$ , the clear kcy C, the error key E, the print key P, and the decimal point key . . The calculator is turned on and off by the switch 5 and the printout is viewed through the magnifying lens window 1.

Referring to FIG. 2, the 18 entry keys 0-9, +, -,  $\times$ , C, E, P,  $\div$ , and a are mounted in the casing 2 above the keyboard encoder 6 in a manner such that the depression of a key causes the key to communicate with conductive strips on the keyboard encoder 6, thereby electrically encoding the key depression so that it can be transmitted to the primary electronics 7 mounted below the encoder 6. The encoder key depression is transmitted from encoder 6 to the primary electronics 7 by the electrical connections 3. The printout tape 14 is arranged in a reel 14' resting on the shelf 10. The printout tape 14 advances from the reel 14' in a vertical position through the guide block 13, which translates the vertical position to a horizontal position so that the tape 14 can advance past the underside of the thermal printer 4 and past the magnifying lens window 1 for

TABLE I

readout of the printed information. Electrical connections 9 provide the electrical communication between the primary electronics 7 and the thermal printer 4. The case 2 is composed of two parts 2' and 2", which may be connected together by hinges and a latch so 5 that part 2' is movable in an upward direction with respect to part 2" in order to allow access to the interior of the casing 2. The power supply batteries 17 and 18, the module 15 containing the auxiliary electronics and the tape advance system 11 are fixed on the floor of the 10 casing 2". A battery charger plug 16 is also provided in the wall of the bottom casing 2". The shelf 10 fits within the bottom casing 2" and rests on the batteries 17 and 18 and module 15 for support. The cutout 10' is provided in the shelf 10 in order to expose the tape 15 bits as shown above one each at the K 4, K 3, K 2, K advance system 11. The tape 14 advances out of the guide block 13 over the resilient pressure pad 19, through the opening 42 and emerges at the exterior of casing 2 through an opening in the side of the casing 2. The physical relationship of the parts is better illus- 20 trated with reference to FIG. 3 in which the tape 14 advances out of the guide block 13 over the pressure pad 19 through an opening 42, the thermal printer 4 being positioned above the pressure pad in a manner that the printing takes place at the underside of the printer 4 25 above the pressure pad 19. Whereas, the information is printed on the top surface of the paper 14 and is viewed from the window 1 to the left of the printer 4. An insulating plexi glass protective cover plate 8 is mounted above the shaft 10 to separate the shelf 10 30 from the primary electronics 7. Electrical connections are provided between the power supply batteries 17 and 18 and the auxiliary electronics contained in module 15 on the floor of the bottom casing 2" which are in turn electrically connected to the primary electron- 35 ics 7 through wires 12 and on/off switch 5.

According to the present invention, the mechanical and electrical parts and their relationship are so adapted with regard to each other so as to provide a very small compact portable calculator of mechanical and operational simplicity and having a high degree of calculating capability which was only before obtainable in calculators of much larger size. For example, according to the described embodiment of the invention, the outside dimensions of the exterior casing 2 are 41/4 inches by 61/8 inches by 13/4 inches and the calculator weights 45 ounces thereby providing a miniature portable electronic calculator of pocket-size dimensions.

The individual parts of the calculator will now be described so that their relationships may be better understood.

# Keys (23) and Keyboard Encoder (6)

The 18 keys provide the means for entering the digits 0-9 and the various commands into the calculator. The depression of a key communicates with the keyboard encoder in the manner to provide a unique electrical signal indicative of the information inscribed on the selected key. In this example, the calculator uses the excess 3 binary decimal code and the encoder directly encodes a key depression into this code. That is, the binary representation of each of the 10 numeric entries is 3 larger than it would be in the conventional binary code. The following Table I illustrates the excess 3 binary decimal code by showing the decimal number entry of a key depression in relation to its binary representation in the excess 3 binary decimal code.

| Decimal Number | Binary Representation |

|----------------|-----------------------|

| 0              | 0011                  |

| 1 .            | 0100                  |

| 2              | 0101                  |

| 3              | 0110                  |

| 4              | 0111                  |

| 5              | 1000                  |

| 6              | 1001                  |

| 7              | 1010                  |

| 8              | 1011                  |

| 9              | 1100                  |

Thus, each numeric key depression results in 4 binary 1 output terminals of the keyboard encoder 6 illustrates in FIG. 5. A zero in the code is represented by a short circuit to ground. A 1 is represented by the unshorted state of the terminal. The 4 binary bits representing a decimal number are arranged in the order K4, K3, K2,

Referring to FIG. 4, a key 23 is mounted in the casing 2 which is fixed with respect to the keyboard encoder 6. Located on the encoder 6 are conductive strips 32 so that when the key 23 is depressed, the conductive layer 31 electrically short circuits the conductive strips 32. Referring to FIG. 5 and in the case that the key 23 depressed is a numeric 2 entry, the four conductive strips 32 associated with the number 2 are short circuited resulting in the terminals KBN, K4, K2, and COM being short circuited to provide the desired encoded entry into the calculator.

The COM conductive strip is the ground connection. Consequently, the K4 terminal is shorted to ground and represents zero in the binary code, the K3 terminal is not shorted to ground and represents 1 in the binary code, terminal K2 is shorted to ground and represents zero in the binary code and terminal K1 is not shorted to ground and represents 1 in the binary code.

The KBN, K4, K2, and COM commands will then be transmitted to the primary electronics 7. In like manner, the other key entries will be encoded by the encoder 6 and transmitted to the primary electronics 7.

The casing 2 is provided with holes respectively accommodating the keys. Referring to FIG. 4, the hole in the casing 2 comprises two sections, the top section having a smaller diameter than the bottom section. The bearing 33 is secured within the smaller diameter section of the hole in casing 2 and extends above the casing 2. The key shaft 26 is movably positioned within a central opening in the bearing 33. Affixed to the key shaft 26 is the key shaft head 24 which provides a convenient surface on which is affixed the key cap 25. A helix spring 27 is positioned between the key shaft head 24 and the casing 2 to provide upward biasing on the cap 24 so that when the pressure is released, the key returns to its normal position leaving the conductors 32 unshorted. Affixed to shaft base 29 is a resilient pad 30 having a thin gold plated copper strip 31. Guide pins 28 are fixed in anchor holes in the casing 2 and slidably mounted in openings in the cap 25. The guide pins 28 prevent rotational movement of the key shaft 26.

FIG. 5 illustrates the keyboard encoder 6 which comprises an insulating substrate on which is located the illustrated pattern of conductive strips. The symbols **0–9,** C, E, P,  $\div$ , .,  $\times$ , –, and + correspond to the like

symbols on the caps of the keys shown in FIG. 2 in the manner that the numeric 2 entry of key 23, for example, shorts out the group of conductive strips 32 associated with the 2 in FIG. 5.

The keyboard encoder 6 accomplishes in substantially one plane the generation of unique electrical signals at its output terminals corresponding to the selected information inscribed on the caps of the keys.

The following Table II illustrates the relationship benals of the keyboard encoder 6 of FIG. 5.

TABLE II

| Key Depressed    | Terminals Shorted    |

|------------------|----------------------|

| 0                | KBN, K4, K3, COM     |

| 1                | KBN, K4, K2, K1, COM |

| 2                | KBN, K4, K2, COM     |

| 3                | KBN, K4, K1, COM     |

| 4                | KBN, K4, COM         |

| 5                | KBN, K3, K2, K1, COM |

| 6                | KBN, K3, K2, COM     |

| . 7              | KBN, K3, K1, COM     |

| 5<br>6<br>7<br>8 | KBN, K3, COM         |

| 9                | KBN, K2, K1, COM     |

| -                | KOP, COM             |

| P                | KOP, P. COM          |

| Ē                | KOP, E, COM          |

| č                | KOP, C, COM          |

| C<br>÷           | KOP, ÷, COM          |

| ×                | KOP, ×, COM          |

| <u> </u>         | KOP, –, COM          |

| +                | KOP, +, COM          |

A detailed description of the keys and keyboard encoder is found in copending U.S. patent application Ser. No. 671,805, filed Sept. 29, 1967, abandoned and refiled Nov. 12, 1970 as continuation application Ser. No. 089,016, now U.S. Pat. No. 3,696,411, entitled Keyboard Encoder filed by Jack S. Kilby and James H. VanTassel and assigned to the assignee of the present application. Said copending application by Jack K. Kilby and James H. VanTassel is incorporated herein by reference.

#### Thermal Printer 4

The thermal printer 4 comprises a  $3 \times 5$  array of integrated semiconductor heater elements located in thermal communication with the tape 14 which is thermally sensitive material that changes color upon the application of heat thereto. The thermally sensitive tape 14 may be the commercially available paper marketed under the trade name "Thermofax" by Minnesota Minning and Manufacturing Company. FIG. 6 illustrates a  $3 \times 5$  array of means located within the window 50 in a semiconductor wafer 48. Each heater element of the 3 × 5 array comprises a monocrystalline semiconductor body in a mesa shape and contains a heater element formed therein at the side of the mesa adjacent the 55 larger insulating support 49 so that when the heater element is energized a "hot spot" is formed at the surface of mesa to provide a localized dot on the thermally sensitive material 14. A group of selectively energized heater elements forms a group of dots on the thermally sensitive material 14 thereby defining a numeric character 0-9 or symbols C, E, P, .,  $\div$ ,  $\times$ , -, + which is printed on the thermally sensitive material 14. The mesas comprising the heater element array are airisolated from each other and joined by a metallic connecting pattern located between the mesas and the insulating support 49 which pattern interconnects the heater elements in the mesas in the desired circuit con-

figuration. A drive matrix for selectively energizing the heater elements and supplying the desired power to them is located in the semiconductor wafer 48 in the area generally designated 51. The circuit elements forming the drive matrix are integral within the semiconductor wafer 48, PN junction isolated from one another and interconnected in the desired configuration by a metallic connecting pattern between the semiconductor wafter 48 and the insulating support 49. The tween a key depression and the shorted output termi- 10 heating element array and the drive matrix are also interconnected in the desired circuit configuration by the metallic connecting pattern between the semiconductor wafer 48 and the insulating support 49. The surface of the printer 4 illustrated in FIG. 6 corresponds to the - 15 bottom surface of the printer 4 illustrated in FIG. 3. That is, the surface of the printer 4 illustrated in FIG. 6 is adjacent the surface of the thermally sensitive material 14 and the thermally sensitive material 14 is in direct contact with the surface of the semiconductor 20 wafer 48 illustrated in FIG. 6.

> Referring to FIG. 6, 52, 53 and 54 are openings in the insulating support 49 so that external connections can be made to the heater element array and drive matrix from the surface of the insulating support 49 which is 25 remote from the semiconductor wafer 48. These openings 52-54 are aligned with bonding pads on the metallic connecting pattern between the semiconductor wafer 48 and the insulating support 49. A conductive pattern is applied onto the surface of the insulating support 49 which is remote from the semiconductor wafer 48. Electrical connections are made to this conductive pattern and to the primary electronics 7 by way of the electrical connections 9 illustrated in FIG. 2.

FIG. 7 illustrates the semiconductor wafer 48 in an intermediate stage of its manufacture in order to show the layout of circuit elements formed in the semiconductor wafer 48 by utilizing the planar process which circuit elements comprise the heater element array and the drive matrix therefor.

Referring to FIG. 7, a  $3 \times 5$  array of transistorresistor pairs is formed on the surface of the P-type semiconductor wafer 48 in the area designated 50 which corresponds to the area of the window 50 in FIG. 6. The heater element array comprises the diffused transistor-resistors pairs, i.e. triple diffused NPN transistors T1 through T15 and their respective N-type diffused resistors R 1 through R 15. Each resistor R1 through R 15 has one of its ends integral with the collector of its respective transistor in the manner that the resistor is ohmically connected to the collector of its corresponding transistor internally of the semiconductor material. The drive matrix for the heater element array comprises 15 triple diffused NPN transistors T 16 through T 30 and their respective diffused N-type collector resistors  $R_{C16}$  through  $R_{C30}$  having one of their ends integral with the collectors and ohmically connected therewith internally of the semiconductor material. The drive matrix also includes 15 diffused P-type base resistors and 15 diffused P-type emitter resistors associated with the 15 transistors T 16 through T 30. Each P-type base and emitter resistor is surrounded by an N type isolating region whereby the insulating PN junctions isolate it from the other circuit elements and from one another. Diffused N-type conductive tunnels  $T_{B1}$  through  $T_{B15}$  are provided in the surface of the semiconductor wafer 48 to allow interconnection between the base electrodes of the transistors T 1 through

T 15 and the emitter electrodes of the transistors T 16 through T 30.

Diffused N-type conductive tunnel  $V_c$  is provided in the surface of the semiconductor wafer 48 in order to interconnect the free end of the resistors R 1 through 5 R 15 and the common terminal  $V_C$ , of the resistors  $R_{C21}$ through R<sub>C30</sub>. Three diffused N-type conductive tunnels PG are provided in the surface of the semiconductor wafer 48 to respectively interconnect one end of the base resistors  $R_{B16}$  through  $R_{B20}$ ,  $R_{B21}$ ,  $R_{B25}$  and  $R_{B26}$ through  $R_{B30}$ . One end of the three tunnels PG will be interconnected by a metallic strip to provide a common terminal PG. A metallic connecting pattern is placed on an insulating layer on the surface of the semiconductor wafer 48 of FIG. 7 in order to connect the cir- 15 cuit elements in the desired circuit arrangement which is illustrated in FIG. 8. The printer 4 comprises 15 mesas and associated drive circuitry and two of the mesas and their associated drive circuitry are illustrated in FIG. 8 for simplicity. The printer 4 therefore 20 comprises 15 inputs for selectively energizing the  $3 \times$ 5 heater element array, a ground input, a collector voltage biasing input  $V_c$  (+ 3 volts) and the PG input. The PG input is the print command and allows the heater element array to be selectively energized.

Referring to FIG. 8, two of the 15 inputs are shown as input 29 and input 30 which are respectively connected to the base electrodes of the drive transistors T 29 and T 30. The PG input is connected to each of the base electrodes of the drive transistors T 30, T 29 re- 30 spectively by way of the base resistors R<sub>B30</sub>, R<sub>B29</sub> in a manner that, when positive pulses concurrently appear at terminals PG and one of the input terminals for example input 30 the selected drive transistor in this case T 30 is energized and triggers the transistor T 15 in the  $\,^{35}$ selected mesa. Accordingly when positive pulses concurrently appear at a terminal PG and terminal input 30, the transistor T 30 is triggered on thereby raising the voltage at its emitter to cause the transistor T 15 to trigger on and draw current through the resistor R 15 thereby causing the hot spot. The concurrent appearance of a positive pulse at terminal PG and at a group of input terminals causes a selected group of mesas to be heated and print out the desired character or symbol.

A detailed description of the thermal printer is found in copending U.S. patent application Ser. No. 671,821, now U.S. Pat. No 3,501,615 entitled "Integrated Heater Element Array and Drive Matrix by Merryman et al., filed Sept. 29, 1967 and assigned to the assignee of the present application (U.S. Pat. Nos. 3,571,917 and 3,601,669 also issued from Ser. No. 671,821 by divisional applications filed May 7, 1969). Said U.S. Pat. No. 3,501,615 by Merryman et al is incorporated herein by reference.

# Tape Advance System 11

The tape advance system 11 advances the tape 14 to a new position a predetermined time after a number or symbol is printed on the tape 14 in response to an electrical command signal. Referring to FIG. 2, the tape advance system 11 comprises support frame 45 secured to the bottom casing 2", magnetic coil 35 secured in the support frame 45, the pole piece 46 secured within a central opening in the coil 35 and having one end secured to the magnetic coil 35 so that the pole piece 46 firmly secures the magnetic coil 35 in the support

8

frame 45, and upper frame member 20 on which is secured the plate 44, having the resilient pressure pad 19. The tape 14 passes over and in contact with the resilient pressure pad 19 and then through the opening 42. Tha tape advance system 11 is illustrated in FIG. 3 without the support frame 45 for simplicity.

Referring to FIG. 3, the pole piece 46 illustrated in FIG. 2 has its end secured to the end section 34, which has a larger diameter than the central opening in the 10 coil 35. The clapper 36 comprised of ferro-magnetic material is pivoted at the point 37 which is fixed to the support frame 45 so that when the magnetic coil 35 is actuated in response to an electrical signal, a magnetic field is created which attracts the clapper 36 and pulls it toward and against the end section 34. Clutch 40 is pivotally mounted on the clapper 36 at point 43. Clutch spring 39 is secured to the clapper 36 at point 41 and contacts the clutch 40 to bias it toward clapper 36. The parts 36, 40, and 39 of FIG. 3 are illustrated in their normal position. That is, the magnetic coil 35 is unactuated. When an electrical signal is applied to coil 35 in order to actuate it, a magnetic field is created attracting clapper 36 toward end section 34. The abrupt movement of clapper 36 causes clutch 40 to be thrust away 25 from clapper 36 and out of contact with the tape 14 as the clapper 36 pivots. When the clapper 36 stops against end section 34, the momentum of the clutch and the force exerted by the clutch spring 39 force the edge of clutch 40 into contact with tape 14. The tape 14 is thus gripped between the clutch 40 and the clutch plate 38. The magnetic field created by the coil 35 is sufficient to move the clapper 36 toward the end section 34 against the biasing of drive spring 22. When the electrical signal applied to the coil 35 is removed and the magnetic field collapses, the drive spring 22 pushes the clapper 36 away from the end section 34 and the tape 14 gripped between the clutch 40 and the clutch plate 38 is advanced in the direction of the arrow by an amount proportional to the clapper stroke, that is, the extent to which the clapper 36 moves away from the end section 34. The speed with which the magnetic field collapses when the electrical signal applied to coil 35 is removed causes the clapper 36 to abruptly thrust forward in the direction of the arrow under the pressure of spring 22. Consequently, the tape 14 is quickly advanced forward in a stepwise fashion in response to electrical signals applied to the coil 35.

FIG. 19 illustrates the drive spring 22 mounted within a lengthwise hole 21 in the upper frame member 20. Whereas, the spring 22 contacts the clapper 36 during the normal position of the tape advance system and is depressed inwardly of the past 20 when the coil 35 is activated and the clapper attracted. A screw can be provided in a larger hole in the clapper 36 extending into the upper frame 20 so that the clapper stroke moving away from the end section 34 will be limited or stopped at a predetermined stroke distance. The coil 35 will comprise two terminals for the electrical input signal, one being grounded.

The guide block 13, thermal printer 4, lens window 1, plate 44, opening 42, and tape 14 are illustrated in FIG. 3 in their relative physical positions to illustrate their mechanical arrangement within the calculator.

A detailed description of the tape advance system 11 is found in copending U.S. patent application Ser. No. 671,804, now U.S. Pat. No. 3,520,459 entitled "Tape Advance System" by John McCrady filed on even date

herewith and assigned to the assignee of the present application. Said U.S. patent application by John McCrady is incorporated herein by reference.

### Power Supply (17, 18) and Auxiliary Electronics (Module 15)

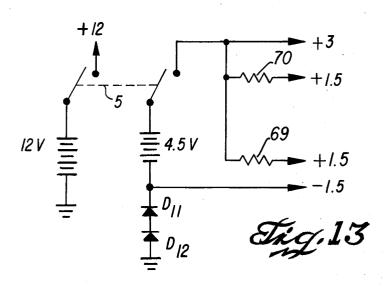

The power supply comprises three 1½ volt batteries 17 connected in series as illustrated in FIG. 2 to provide the 4½ volt power source illustrated in FIG. 13 and eight 1½ volt batteries 18 connected in series as il- 10 lustrated in FIG. 2 to provide the 12 volt power source illustrated in FIG. 13. Referring to FIG. 13, the 4, 5 volt power source is connected to the auxiliary electronics module 15 and through the switch 5 corresponding to electronics 7, which will be described later.

The auxiliary electronics module 15 contains the circuit components and their interconnections as is illustrated in FIGS. 9-12. Referring of FIG. 9, the terminal marked +3 volts is connected to the +3 volt terminal 20 illustrated in FIG. 13, and the terminals marked OS 1, OS 2, OS 3, OS 4, OS 5, OS 6, OS 7, PG, PG T, and ADV are connected to the similarly marked terminals of the primary electronics 7 through the connection 12 of FIG. 2 as will be described later. Referring to FIG. 25 10, the terminal marked +12 volts is connected to the +12 volt terminal of FIG. 13, the terminal marked SOL is connected to the magnetic coil or solenoid 35 of the tape advance system 11 illustrated in FIGS. 2 and 3, and the terminal marked ADV is connected to a similarly marked terminal of the primary electronics 7 as will be described later. Referring to FIG. 11, the terminals marked E 1 and E 2 are connected to similarly marked terminals of the primary electronics 7 as will be described later. Referring to FIG. 12, the terminal  $-1.5^{-35}$ volts is connected to the 4.5 volt power source illustrated in FIG. 13 wherein the diodes D 11 and D 12 of FIG. 12 are also illustrated.

The interconnected circuit elements of FIG. 9 supply the R-C time delay networks for three one-shot multivibrators used in the printing sequence to be described later. The circuit of FIG. 10 provides a buffer for receiving the command ADV from the primary electronics and converting it into the appropriate voltage SOL for application to the magnetic coil 35.

## Primary Electronics 7

The primary electronics of the calculator is embodied in an integrated semiconductor circuit array located in substantially one plane. The integrated semiconductor circuit array comprises the control and arithmetic sections of the calculator for performing the arithmetic operations of the numbers entered into the calculator and generating the control and timing signals for appropriately carrying out the arithmetic operations, the printout of the entry data and answers and the advancement of the tape. The integrated semiconductor circuit array is mounted parallel with the keyboard encoder 6 so that they occupy generally parallel planes one above the other in a manner that the entry encoding and control and arithmetic operations of the calculator are accomplished in a very small compact space.

The various key entries are made, electrically encoded by the keyboard encoder 6 and transmitted to the integrated semincoductor circuit array where the various arithmetic calculations are made and control

signals generated for appropriately commanding the thermal printer 4 and the tape advance system 11.

The integrated seminconductor circuit array is illustrated in FIG. 14 and comprises four integrated semiconductor circuits placed in the areas designated 73-75, three integrated semiconductor shift registers SR 1, SR 2, and SR 3 and two resistors 69, 70 all interconnected and arranged on the insulating substrate 7' in the manner to be described.

FIG. 15 illustrates a logic diagram having 151 functional unit NAND gates interconnected in the manner illustrated and embodied in the integrated semiconductor circuit whose substrate is mounted in the area designated 75 in FIG. 14. FIG. 16 illustrates a logic diagram switch 5 illustrated in FIGS. 1 and 2 to the primary 15 having 132 functional unit NAND gates interconnected in the manner illustrated and embodied in an integrated semiconductor circuit whose substrate is mounted in the area designated 74 in FIG. 14. FIG. 17 illustrates a logic diagram having 135 functional unit NAND gates interconnected in the manner whose substrate is mounted in the area designated 72 in FIG. 14. FIG. 18 illustrates a logic diagram having 116 functional unit NAND gates interconnected in the manner illustrated and embodied in an integrated semiconductor circuit whose substrate is mounted in the area designated 73 in FIG. 14.

Each NAND gate of FIGS. 15-18 is identically constructed and comprises the circuit illustrated in FIG. 20. The NAND gate contains 6 PNP transistors, 2 NPN transistors, and 2 resistors interconnected in the manner illustrated in FIG. 20 with 6 input terminals, a ground terminal and a collector voltage terminal +3 volts. Transistor T 35 has its collector and base electrodes short circuited and acts as a PN junction diode connected between resistor R 33 and the base of transistor T 34; the emitters of the PNP transistors are connected to the base of transistor T 35 and their collectors are connected to ground, so that when a zero or ground appears at any of the input terminals, a PNP transistor is conducting and transistor T 35 is reversed biased, causing transistor T 34 to be off and the output terminal, to be in the high, or one, state. When ones, or positive voltages appear at all the input terminals, the reverse bias is removed from transistor T 35, which turns transistor T 34 on drawing current through resistor R 33A which causes the output terminal to be in the low or zero state. Not all of the input terminals of the circuit of FIG. 20 are used by all of the gates of FIGS. 15-18 and only those input terminals which are used are illustrated in FIGS. 15-18. For example, referring to FIG. 15, gates 1-8 within the block 306 each utilize two input terminals, while gates 80-87 within the block 303 each utilize four input terminals.

Moreover, the functional unit NAND gates in some instances are interconnected, one NAND gate with another, to form multivibrators and counters such as the NAND gates interconnected as illustrated within the block 317 of FIG. 17 to form a flip-flop and the NAND gates interconnected as illustrated within the block 312 of FIG. 18 to form a 16 position counter.

Each integrated semiconductor circuit emobdying the logic circuits of FIGS. 15-18 is formed in the surface of a silicon substrate of P-type conductivity of the desired resistivity utilizing the planar process in which a silicon oxide film is thermally grown on the silicon substrate by placing it in a furnace at an elevated temperature and passing an oxidizing agent over it. The re-

sulting silicon oxide film acts as a masking medium against the impurities which are later diffused into the substrate. Holes are produced in the oxide film to allow subsequent diffusion processes to form the transistors, resistors, and PN junction isolating functions. These 5 holes which are patterns of the desired circuit elements and PN junction isolating regions are produced by photolithographic techniques. Contacts and interconnections between the circuit elements are made by similar photolithographic techniques using for example a 10 molybdenum-gold-molybdenum (Mo-Au-Mo) contact system over the oxide film to form a metallic pattern connecting the circuit elements together in the circuit configuration of FIG. 20, thereby forming the NAND gates which are to be interconnected in the logic cir- 15 cuits of FIGS. 15-18. The metallic pattern comprises conductive strips on the oxide film extending onto openings in the oxide film for connecting the circuit elements into the circuit configuration of FIG. 20 and comprises contact areas which are to be intercon- 20 15-18. Conductive strips are provided in one direction nected to result in the logic circuits of FIGS. 15-18.

FIG. 29 illustrates the P-type silicon substrate 89 of desired resistivity on whose surface the NAND gates 90 are formed. FIG. 30 illustrates the top view of one of the NAND gates 90 formed on the surface of the sub- 25 strate 89 and the metallic interconnection pattern interconnecting the circuit elements of the NAND gate in the desired configuration of FIG. 20. The NAND gate 90 comprises six double diffused PNP transistors 91 through 96 two triple diffused NPN transistors T 34, 30 T 35 and a diffused N-type resistor R 33, R 33A having a center tap 97 for the application of the +3 volts. The P-type collectors of the transistors 91 through 96 are integral and all interconnected within the P-type substrate 89 while the P-type substrate 89 is connected to 35 ground by the metallic strip 100 ohmically engaging the top semiconductor surface of the substrate 89. The PNP transistor 93 for example comprises as its collector the P-type substrate 89, the N-type diffused base region 93B and the P-type diffused emitter region 93E. 40 The construction of the other PNP transistors of the NAND gate 90 are the same. The construction of the transistors T 34 and T 35 are similar and T35 comprises the diffused N-type collector region T 35C which is diffused at the same time as the N-type diffused resistors 45 R 33, R 33A, the N-type collector of T 34 and the Ntype base regions of transistors 91-96. Transistor T 35 further comprises the diffused N-type emitter region T 35E. The emitters of transistors 91-96 are all connected together and connected to the base of transistor T 35 by conductive strip 99. Referring to FIG. 31 it can be seen that the conductive strip 99 short circuits the collector-base PN junction of transistor T 35. The emitter of transistor T 35 is connected to the base of transistor T 34 by conductive strip 101. Expanded metallic contacts terminating in enlarged contact areas and labeled input in FIG. 30 are connected respectively to the base zones of the transistors 91-96. An expanded metallic contact terminating in an enlarged contact area and labeled output is connected to the collector electrode of transistor T 34. Accordingly, the NAND gate 90 is interconnected in the circuit configuration of FIG. 20 and there are 6 metallic contact areas on the silicon oxide film for the input terminals (input), a metallic contact area on the silicon oxide film for the ground connection (strip 100), a metallic contact area on the silicon oxide film for the output connection

(output), and a metallic contact area on the silicon oxide film for the application of the +3 volts (+3volts). The circuit elements of each NAND gate of the integrated semiconductor circuit are interconnected in this manner at a first level of interconnections.

FIG. 31 illustrates a cross section of FIG. 30 taken along the line A—A. Referring to FIG. 31 there is illustrated the triple diffused NPN transistor T 35, the silicon oxide film SiO2 on the surface of the silicon substrate 89, and first level metal contacts 99 and 101 extending into openings in the silicon oxide film and connecting to the emitter and shorting the collector base PN junction. Additionally shown in FIG. 31 are second and third levels of interconnections represented by second and third insulating layers labeled sputtered SiO<sub>2</sub>. After the circuit elements are interconnected to form the separate NAND gates, the NAND gates are then electrically interconnected at a second and third level of interconnection to form the logic circuits of FIGS. at the second level of interconnections, for example North-South and conductive strips are provided at a perpendicular direction East-West at a third level of interconnections to interconnect the NAND gates into the logic circuits of FIGS. 15-18. FIG. 31 illustrates the second level of interconnection provided by an insulating film over the first level of interconnections and the conductive strips 130, 131, and 132 extending in one direction. Thereafter a third layer of insulating material is provided over the second level of interconnections and conductors are provided thereon extending in a perpendicular direction to the second level conductors. The second and third level insulating films may be RF sputtered silicon dioxide and similar photographic techniques may be utilized to form openings in the RF sputtered silicon dioxide and expose the contact areas for interconnecting the NAND gates.

A detailed description of the processes of forming the interconnected functional unit NAND gates at a first level of interconnections and interconnecting the NAND gates in the desired logic configuration at a higher level of interconnection is found in copending patent application Ser. No. 645,539, now U.S. Pat. No. 3,643,232, filed June 5, 1967, entitled "Method of Making Semiconductor Devices" by Jack S. Kilby (which was a continuation of Ser. No. 420,031, filed Dec. 21, 1964, now abandoned) which is assigned to the assignee of the present application. Said copending patent application by Jack S. Kilby is incorporated herein by reference.

A detailed description of the molybdenum-goldmolybdenum multi-level contact system for interconnecting circuit elements of an integrated semiconductor circuit is found in copending patent application Ser. No. 606,064, filed Dec. 30, 1966, entitled "Ohmic Contact and Multi-Level Interconnection System for Integrated Circuits" by Clark et al. and assigned to the assignee of the present application, said application Ser. No. 606,064 having been abandoned and refiled Jan. 2, 1969 as Ser. No. 791,862, now U.S. Pat. No. 3,581,161. Said copending patent application Ser. No. 606,064 (and resulting Patent) by Clark et al is incorporated herein by reference.

Accordingly, four integrated semiconductor circuits are formed embodying respectively the logic circuits of FIGS. 15-18 and having terminals or contact pads on the third level insulating film around the periphery of the silicon substrate corresponding respectively to the terminals around FIGS. 15–18. For example, referring to FIG. 15, the terminals or contact pads of the integrated semiconductor circuit correspond to the terminals marked K 1, K 2, ... RL, GKC, G2E, ... ADS, 5 CP 3, ... L1.

Referring to FIG. 14, the integrated semiconductor circuit array comprises an insulating substrate 7' having printed conductors on its top and bottom surface in order to effect the desired interconnections between 10 the integrated semiconductor circuits. Four insulating plates 76, 77, 78 and 79 respectively having apertures therein 80, 81, 82 and 83 are mounted side by side on the insulating substrate 7' over some of the printed conductors on the top surface of the insulating sub- 15 strate 7'. The insulating plates 76, 77, 78 and 79 have respective apertures therein 80, 81, 82 and 83 for respectively accommodating the integrated semiconductor circuits embodying the logic circuits of FIG. 17, 18, 16 and 15. Patterned conductors 84, 85, 86 are applied 20 onto the top surface of the insulating plates 76, 77, 78 and 79 and overhang into the apertures 80, 81, 82 and 83 and onto the top surface of the insulating substrate

The insulating plate 76 for example, its associated 25 patterned conductors and integrated semiconductor circuit are assembled as follows: An insulating plate 76 having an aperture 80 is provided. A thin continuous sheet of metal is bonded onto the top surface of the insulating plate 76 such that the metal sheet extends over 30 the opening 80 and extends over one side of the insulating plate 76. Photoresist material is applied over both sides of the metal sheet and the photoresist material on the top side of the metal sheet is then patterned and the metal sheet etched such as by conventional photolitho-  $^{35}$ graphic and etching techniques to form lead strips overhanging the opening 80 and overhanging one side of the insulating plate 76 i.e. the side adjacent SR 1. The semiconductor circuit having its three levels of interconnections is inserted into the opening 80 from the bottom of the insulating plate 76 and the bonding pads on the surface of the third level of interconnections are aligned with and bonded to the overyhanging lead strips utilizing conventional ultrasonic bonding techniques for example. The thickness of the semiconductor substrate of the integrated semiconductor circuit is less than the thickness of the wall of the opening 80 in the insulating plate 76 so that the bottom of the semiconductor substrate does not touch the top surface of the insulating substrate 7' when the insulating plate 76 50 is mounted thereon. Alternately, an insulating layer may be provided on the bottom surface of the semiconductor substrate so that it is electrically isolated from any printed conductors on the top surface of the insulating substrate 7' that may extend between the semiconductor substrate and the top surface of substrate 7'.

The integrated semiconductor circuits embodying the logic circuits of FIGS. 15 and 17 are respectively mounted within the openings 83 and 80 in the manner that terminals ADS, SUB, ... G2K, G2E, of FIGS. 15 are adjacent the corresponding terminals ADS, SUB, ... G2K, G2E of FIG. 17. The integrated semiconductor circuits embodying the logic circuits of FIGS. 16 and 18 are respectively mounted within the opening 82 and 81 in a manner that the terminals RDM, RMD, ... CL, CZO of FIG. 16 are adjacent the corresponding termi-

nals RDM, RMD, . . .  $\overline{\text{CL}}$ ,  $\overline{\text{CZO}}$  of FIG. 18. Consequently, the terminals L 1, L 3, . . . CO, CP 3 of FIG. 15 are adjacent the corresponding terminals L 1, L 3, . . . CO, CP 3 of FIG. 16 and the terminals PRC, DTP, . . . AS, G2E of FIG. 17 are adjacent the corresponding terminals PRC, DTP, . . . AS, G2E of FIG. 18.

The assembled insulating plates 76–79, patterned conductors 84, 85, 86, and integrated semiconductor circuits are then mounted side by side on the top surface of the insulating substrate 7' as illustrated in FIG. 14. Each integrated semiconductor circuit comprises a plurality of horizontal rows of NAND gates and a like plurality of conductive ground strips 100. See FIGS. 29 and 30. At the third level of interconnections all the rows of ground strips are interconnected by an overlying perpendicular ground strip which is brought out to a patterned conductor ground strip on the insulating plate which is schematically illustrated as the ground connection on each of the insulating plates 76–79. The patterned conductors 84, 85, are respectively connected to each other at the interfaces of the insulating plates 76-79 and the patterned conductors 86 overhanging the insulating plates 76-79 onto the top surface of the insulating substrate 7' are connected to printed conductors on the top surface of the insulating substrate 7'.

Accordingly, the bonding or contact pads on the third level of interconnections of the integrated semi-conductor circuits are electrically connected to the similarly marked terminals of FIGS. 15-18 by way of the patterned conductors 84, 85 while the terminals K 1, K 2, ... RL, GKC of FIG. 15, the terminals DZ, DEC, ... J, C of FIG. 17, the terminals DPT, KOP, ... RL, GKC of FIG. 18 and the terminals CP 1, DZ, ... KBC, ADV of FIG. 16 are electrically extended to the top surface of the substrate 7' at the terminals 86 and similarly marked terminals are interconnected by printed conductors on the substrate 7'.

A detailed description of the assembly and mounting of an insulating plate 76 for example, its overhanging patterned conductors and associated integrated semi-conductor circuit is found in copending patent application Ser. No. 568,799 filed July 29, 1966 entitled "Process for Packaging Multi Lead Semiconductor Devices and REsulting Products" by Jack S. Kilby et al, now U.S. Pat. No. 3,484,534, which is assigned to the assignee of the present application. Said copending patent application by Jack S. Kilby et al. is incorporated herein by reference.

The primary electronics 7 additionally contains three 24-bit shift register SR 1, SR 2, and SR 3. These shift registers are identical and each one contains four 6-bit rows in parallel so that the four binary bits representing a numeric entry are entered in parallel and associated input/output circuitry as illustrated in FIG. 22. Therefore, each shift register, SR 1, for example, contains the four groups of 6 shift register bits, associated input circuitry T 40 through T 47, R 40 through R 47, and RB 40 through RB 46 associated output circuitry T 48 through T 55 and R 48 through R 55.

A binary 1 or 0 is applied to the input terminals I 40, I 42, I 44, I 46 for entry into the shift register. A binary 1 (positive pulse) at iput terminal 40, for example, turns transistor T 40 on and transistor T 41 off, so that the collector voltage of transistor T 40 is low in realtionship to the collector voltage of transistor T 41 for entering a 1 into the shift register.

The circuitry of the shift register is illustrated in FIG. 21, wherein the binary information entered into one storage unit flip flop FF 1 is transferred to another succeeding storage flip flop FF 3 by means of the intermediate storage unit flip flop FF 2 under control of the 5 clock pulse CPO. Binary information is transferred from one storage unit to another in the shift register by two phase clocking action, whereby under one condition of the clock pulse, CPO, the binary information in unit FF 2 and under a second condition of the clock pulse CPO, the binary information is transferred out of the intermediate storage unit FF 2 into the succeeding storage unit FF 3. One bit of the shift register comprises the storage unit FF 1, and the intermediate storage unit 15 FF 2. Gates 110 and 111 are arranged between a storage unit FF 1, or FF 3 and an intermediate storage unit, FF 2, for blocking and permitting electrical communication between the storage units and effecting the transfer of the binary information in the shift register 20 FF 2 of FIG. 21 in the surface of a P-type silicon subunder control of the clocking pulse CPO.

The voltage level of the clock pulse CPO varies from +1 volts to -1 volts, the +1 volt condition being its normal state. When CPO is at +1 volts, the collector voltate storage unit FF 2 are positive and cause gate 111 to be in a blocking condition, so that there is no communication between the intermediate storage unit FF 2 and the succeeding storage unit FF 3, while the biasing of gate 110 is such that there is electrical communication between the storge unit FF 1 and the intermediate storage unit FF 2, so that the binary information contained in storage unit FF 1 is transferred to the intermediate storage unit FF 2, When CPO is at -1 volts, the collector voltages of transistors T 65 and T 66 are lowered to cause gate 110 to be in a blocking condition in the manner that there is no electrical communication between storage unit FF 1 and intermediate storage unit FF 2 while gate 111 is unblocked and allows electrical communication between intermediate storage unit FF 2 and storage unit FF 3 thereby transferring the binary information out of intermediate storage unit FF 2 into storage unit FF 3. Thus, clock pulse CPO controls the transfer of binary information from one storage unit to another.

A detailed description of the shift register circuit of FIG. 21 is found in copending U.S. Patent application Ser. No. 650,832 filed July 3, 1967, entitled, "Information Transfer System" by Jerry D. Merryman, now U.S. Pat. No. 3,573,754, which application is assigned to the assignee of the present application. Said copending U.S. patent application by Jerry D. Merryman is incorporated herein by reference.

Four binary bits are applied in parallel to the input terminals I 40, I 42, and I 44 and I 46 and through the respective input circuitry of FIG. 22 to the first storage unit of each of the four 6-bit shift registers of FIG. 22.

Referring to FIG. 25, the clock pulse output CPO is 60 applied to the emitters of the intermediate storage units FF 2 between a preceeding FF 1 and succeeding FF 3 storage unit of each of the four rows of storage units in each shift register. A command signal CP 1 or CP 2 which will be described later, is applied to the input of 65 the clock pulse circuit to change the normal +1 volt condition of CPO to -1 volt. Transistors T 60, T 61 and T 62 are normally non-conducting and upon the appli-

cation of a positive pulse CP 1, or CP 2, they are turned on, causing the collector voltage of T 62 to become -1 volt. Each integrated semiconductor shift register circuit SR 1, for example, comprises the four rows of 6 bits and associated input, output circuitry of FIG. 22 and the clock pulse circuit of FIG. 25. Each identical shift register SR 1, SR 2, and SR 3 is fabricated utilizing the planar process as previously described, triple diffusion to form the NPN transistors a single level metallic storage unit FF 1 is transferred to intermediate storage 10 interconnection pattern over the silcon oxide film and conductive tunnels in the surface of the semiconductor substrate at the places where conductive pathways cross over one another as is described in said aforementioned copending U.S. patent application by Jack S. Kilby, and said aforementioned copending U.S. patent application by Jerry D. Merryman.

FIG. 33 illustrates the partial top view of an integrated semiconductor shift register embodying the storage unit FF 1, gate 110 and intermediate storage unit strate 112 of desired resistivity. The 24 bits of the shift register are similarly incorporated in the integrated semiconductor circuit. Referring to FIG. 32, there is illustrated the NPN triple diffused transistors T 63 –T ages of the transistors T 65 and T 66 of the interemedi- 25 66 and the triple diffused NPN gate transistors T 67 and T 68. A storage unit transistor T 65, for example, and a corresponding gate transistor T 67, for example, are formed within a common N-type diffused collector region in the manner that the resistor R 65 has one end ohmically connected to the collector region of transistors T 65 and T 67 within the semiconductor material. All the corresponding storage unit transistors, gate transistors and resistors are similarly constructed in the surface of the semiconductor material. Each gate transistor T 67, for example, has its collector-base PN junction short circuited by conductive strip 113. Gate transistors 114 and 115 are illustrated as being formed within the respective collector regions of storage unit transistors T 63 and T 64. These gate transistors provide the input to the storage unit comprised of transistors T 63 and T 64 in the manner that the collector voltages of the input circuitry, transistors T 40 and T 41 of FIG. 22, are connected respectively to the collector electrodes of transistors T 63 and T 64 by means of the conductive strips 119 and 118.

The metallic interconnection pattern over the silicon oxide film on the surface of substrate 112 comprises conductive strips 113, 117, ground, CPO, interconnecting the circuit elements in the desired circuit configuration. The heavily doped diffused N type conductive tunnel 116 in the surface of the substrate 112 interconnects the two ends of the metallic strips +3 volts, so that the conductive strips, ground and CPO can cross over the conductive tunnel 116, in a manner to allow the 24 bits, gates and clock pulse circuit of the shift register to be interconnected at one level on the silicon oxide film.

FIG. 33 illustrates a cross section of FIG. 32 taken along the lines A-A to show the triple diffused transistors T 63 and 114, having a commmon N type diffused collector region and conductive strip 117 short circuiting the collector-base PN junction of transistor 114.

The metallic interconnection pattern on the silicon oxide film on substrate 112 comprise enlarged contact areas for making external connections to the integrated semiconductor circuit. There are 17 contact areas on the surface of the silicon oxide film comprising the terminals for '1.5 volts corresponding to the similarly marked +1.5 volt terminals of FIG. 21 and FIG. 22, -1.5 volts corresponding to the similarly marked terminals of FIG. 25, CP 1 or CP 2 corresponding to the similarly marked terminal of FIG. 21, and FIG. 22, I 40, I 5 44, and I 46 corresponding to the similarly marked terminals of FIG. 22, and 8 output terinals corresponding to the similarly marked terminals of FIG. 22 and +3 volts corresponding to the similarly marked terminals of FIG. 22 and FIG. 25. The three integrated semiconductor shift registers are encapsulated in a flat package construction with 17 coplanar flat leads respectively connected to the 17 contact areas extending out of the sides of the flat package as is well known in the art.

Referring to FIG. 14, the 3 integrated semiconductor 15 shift registers SR 1, SR 2, and SR 3 are mounted on the surface of the substrate 7' and their leads connected to printed conductors on the substrate 7' to effect the desired interconnections between the shift registers and the other components of the primary electronics 7.

Resistors 69–70 are also mounted on the insulating substrate 7'. Referring to FIG. 13, the 4.5 power source is connected through resistors 69–70 corresponding to the similarly marked resistors 69–70 of FIG. 14 to respectively supply the 1.5 volts to the shift registers SR 25 1, SR 2, through resistor 70 and to SR 3 through resistor 69. The -1.5 and +3 volt terminals of FIG. 13 are also connected to the corresponding terminals of the shift registers SR 1, SR 2, and SR 3.

In order to illustrate the planar form of the primary <sup>30</sup> electronics, the dimensions of the integrated semiconductor circuit array of the described embodiment are 45% by 4 by ½ inches.

Alternatively, the planar integrated semiconductor circuit array may comprise a large integral semiconductor wafer smaller than the insulating substrate 7' comprising quadrants respectively embodying the logic circuits of FIGS. 15-18. The closely grouped circuit elements comprising each functional unit NAND gate at the surface of the integral semiconductor wafer may be interconnected at a first level of interconnections to form the NAND gate, the NAND gates in each quadrant may be interconnected at multi-levels of interconnections to respectively embody the logic circuits of FIGS. 15-18 and the logic circuits of the quadrants may be interconnected at another level of interconnections using RF sputtered silicon oxide, photolithographic techniques and metal deposition techniques as discussed and remaining interconnections effected by printed conductors on the top or bottom surface of the insulating substrate 7'. Moreover, the integral semiconductor wafer may be made larger so that the shift registers SR 1, SR 2, and SR 3 and the two resistors 69-70 may be incorporated into the surface of the larger integral semiconductor wafer with their interconnections being effected at multi-levels of interconnections and remaining interconnections being effected by printed conductors on the insulating substrate 7'.

Moreover, to further reduce the size of the calculator, the insulating substrate of the keyboard encoder 6 may be integrated with the insulating substrate 7' of the integrated semiconductor circuit array such that the conductors 32 of the keyboard encoder 6 occupy one plane surface of a common insulating substrate and the integrated semiconductor circuit array occupies the opposite parallel plane surface of the common insulating substrate with interconnections being effected by

conductive feed throughs extending vertically through the common insulating substrate between the parallel planes, the keyboard encoder effecting the mechanical to electrical conversion of the key entries which in turn are transmitted to the integrated semiconductor circuit array for the arithmetic calculations and the control signals.

Furthermore, the conductive pattern on the keyboard encoder may be simplified to provide a unique short circuit signal indicative of the particular key entry rather than directly encoding the key entry into the excess three binary code and encoding gates provided in the integrated semiconductor circuit array responsive to the unique shorting signal for encoding it into the binary language of the calculator.

Referring to FIG. 24, the shift register SR 3 acts as the operand register of the arithmetic section of the calculator, having the 4 binary bit inputs corresponding to I 40, I 42, I 44, and I 46 of FIG. 22, the 8 outputs terminals corresponding to the output terminals of FIG. 22 and the clock pulse input terminal CP 2 corresponding to the terminal CP 1 or CP 2 of FIG. 25.

Referring to FIG. 23, the shift registers SR 1 and SR 2 are interconnected to act as a 48 bit accumulator register of the arithmetic section of the calculator. Each shift register SR 1 and SR 2 comprises the clock pulse circuit of FIG. 25 and the input terminal of these two clock pulse circuits are connected together to provide the terminal CP 1 corresponding to the input terminal CP 1 or CP 2 of FIG. 25. The accumulator register SR 1, SR 2 comprises the 4 input terminals to shift register SR 1 corresponding to the 4 bits applied at terminals I 40, I 42, I 44 and I 46 of FIG. 22. Four of the eight input terminals of shift register SR 1 corresponding to four marked output terminals of FIG. 22 are connected to the four input terminals corresponding to I 40, I 42, I 44 and I 46 of FIG. 22 in shift register SR 2. The 8 output terminals of shift register SR 2 correspond to the 8 output terminals of FIG. 22. Accordingly, the shift registers SR 1 and SR 2 are interconnected in the manner illustrated in FIG. 23 by means of the printed conductors on the substrate 7' of FIG. 14. The remaining four output terminals of shift register SR 1 are not used.

Referring to FIG. 23, the four bits applied to the input of the accumulator register SR 1, SR 2 are designated A 1, A 2, A 3, and A 4 and are connected to the correspondingly marked terminals A 1, A 2, A 3 and A 4 of FIG. 15 by means of the printed conductors on the substrate 7'. The eight output terminals of the accumulator register SR 1, SR 2 are designated Y 1, Y 1, Y 2, Y 2, Y 3, Y 3, Y 4 and Y 4 are connected to the similarly marked terminals of FIG. 15 by means of the printed conductors on the substrate 7'. The clock pulse terminal CP 1 of the accumulator register SR 1, SR 2 is connected to the similarly marked terminal CP 1 of FIG. 16 by means of a printed conductor on the substrate 7'.

Referring to FIG. 24, the operand register SR 3 comprises 4 input terminals designated 01, 02, 03, and 04, which are connected to the similarly marked terminals 01, 02, 03, and 04 of FIG. 15 by means of printed conductors on the substrate 7'. The 8 output terminals of the operand register SR 3, designated X 1,  $\overline{X}$  1, X 2, X 2, X 3, X 3, X 4 and  $\overline{X}$  4 are connected to the similarly marked terminals of FIG. 15 by means of printed conductors on the substrate 7'. The clock pulse input terminal CP 2 of the operand register SR 3 is connected

to the similarly marked terminal CP 2 of FIG. 18 by means of a printed conductor on the substrate 7'. The interconnected circuit components of the auxiliary electronics module 15 are connected to the compounds of the primary electronics 7 by means of the connections 12.

Referring to the FIG. 9, the terminals marked OS 1, OS 2, OS 3, OS 4, OS 5, OS 6, OS 7, ADV and PGT are connected to the similarly marked terminals of FIG. 18. The terminal marked PG of FIG. 9 is connected to 10 the similarly marked terminal of the thermal printer 4 as illustrated in FIG. 8. The +3 volt terminal of FIG. 9, is connected to the similarly marked terminal of the power source illustrated in FIG. 13.

Referring to FIG. 10, the +12 volt terminal is connected to the similarly marked terminal of the power supply illustrated in FIG. 13. The terminal marked SOL is connected to the magnetic coil 35 of the tape advance system 11. The terminal marked ADV is connected to the similarly marked terminal of FIG. 18.

Referring to FIG. 11, the capacitor C 6 has its terminal E 1, E 2, connected to the similarly marked terminals of FIG. 18.

Referring to FIG. 12, the series connected diodes D 11 and D 12 have their -1.5 volt terminal connected to the 4.5 volt power source illustrated in FIG. 13, wherein the diode D 11 and D 12 are also illustrated.

Referring to FIG. 5, the terminals of the keyboard 6  $_{30}$ marked .. KOP, COM, C, E, P, K 4, K 3, K 1, KBN, K 2, K 1, X, -, +, COM, KOP,  $\div$ , are electrically connected to the components of the primary electronics 7 by means of the electrical connections 3. Whereas, the KBN terminal is connected to the similarly marked ter- 35 minal of FIG. 18, the . terminal is connected to the DPT terminal of FIG. 18, the two KOP terminals are connected to KOP of FIG. 18, the COM terminals are connected to the ground connection of the primary electronics, the C terminal is connected to the terminal 40 marked KBC of FIG. 18, the E terminal is connected to KBE terminal of FIG. 17, the P terminal is connected to the KBP terminal of FIG. 17, and X terminal is connected to the KBM terminal of FIG. 17, the - terminal is connected to the KBS terminal of FIG. 17, the + ter- 45 minal is connected to the KBA terminal of FIG. 17, and the ÷ terminal is connected to the KBD terminal of FIG. 17.

The 15 input terminals of the thermal printer 4 corresponding to the input terminals input 30, 29 of FIG. 8 are connected respectively to the terminals marked A, F, K, L, G, B, H, N, M, I, D, E, O, J, and C of FIG. 17. The PG terminal of the thermal printer 4 corresponding to the similarly marked terminal of FIG. 8 is connected to the similarly marked terminal of FIG. 9. The +3 volt terminal of the thermal printer 4 corresponding to the similarly marked thermal of FIG. 8 is connected to the similarly marked terminal of the power supply illustrated in FIG. 13.

Accordingly, the primarily electronics comprising the arithmetic and control sections of the calculator is embodied in substantially one plane located beneath the encoder keyboard 6 to effect the high degree of electronic calculating capability while being mechanically adapted in relationship to the other parts of the calculator to result in extreme miniaturization and yet retain mechanical and operational simplicity.

# Operation

The calculator, according to the described embodiment, is a binary coded decimal calculator, using the excess three binary decimal code and capable of adding, subtracting, multiplying and dividing with some degree of automatic decimal point placement. Operation is accomplished by means of the 18 keys, (23), and six digits may be entered into the calculator for any one number. The ten numeric keys, 0–9 are used to enter the number into the operand register SR 3. Each numeric key depression results in the corresponding digit being printed on the tape 14, which, consequently, is a record of all entry data, as well as the answers. The operand register, SR 3, comprises 24 bits, representing six digits.

The eight command keys are used to enter various commands into the calculator. The clear key, C, clears all registers in the arithmetic section of the primary electronics 7 and normalizes the circuits. A "C" followed by a space is printed on the tape 14 to record this operation. The add key, +, causes the number in the operand register, SR 3, to be added to that of the accumulator, SR 1, SR 2, and the result is stored in the accumulator register. A plus character followed by a space is printed on the tape 14 to record this operation. The subtract key, -, causes the number in the operand register, SR 3, to be subtracted from that of the accumulator register, SR 1, SR 2 and the result is stored in the accumulator register. A minus character followed by a space is printed on the tape 14 to record this operation. The print key, P, is used to command the printout of whatever number is in the accumulator register, SR 1, SR 2. No special character is printed on the tape 14 to identify the print operation. However, the answer up to 12 numeric digits, plus decimal point, is printed on the tape, followed by two spaces to separate this record from later ones. The print operation does not clear the machine, so that further operations may be made on the number in the accumulator register. The multiply key ×, causes multiplication of the number in the operand register with that in the accumulator register. An X followed by a space and followed by the product which may comprise 12 digits plus decimal point, are printed on the tape 14. The multiplying operation automatically clears the machine, so that further calculations may be made without the use of the C key. The divide key ÷ causes division of the number in the accumulator register by that in the operand register. As in the case of multiplication, printout is automatic and results in the following format: /, space, six digit quotient, space, six digit remainder, two more spaces. The divide operation clears the machine, and no decimal points are printed in a divide operation. To prevent overflow, some degree of alignment of the two numeric entries to be divided is required. A suitable rule to follow is that the two numeric entries to be divided have an exactly equal number of significant digits up to six. Should overflow occur, due to the operator's not following a suitable alignment rule, no numeric answer will be produced, but the machine will be cleared and a C will be printed on the tape. The error key, E, is used to clear the contents of the operand register, SR 3, when an incorrect number has been entered. An E and a space will be printed after the faulty entry. This operation does not disturb the accumulator register. The decimal point key is used to insert decimal points in the

22

entry numbers. There are seven valid locations for the decimal point on entry: before any of the digit entries; after all of the digit entries; or at any of the five places between the six permissible digit entries. In multiplication, the two numbers to be multiplied may have different positions of the decimal point. In addition and subtraction, the numbers to be added or subtracted should comprise the same number of digits following the decimal point. In any operation, if no decimal points are placed in the entry data, the numbers are treated as 10 whole numbers, and the answer will contain no decimal point. In divide operations, a decimal point will not appear in the answer. However, if desired for record purposes, the entry data may contain decimal points, but these will be ignored by the calculator.

The use of the calculator for add, subtract, multiply, and divide, correlated with the suitable key depressions, is summarized as follows:

## Addition

C, Clear (if necessary)

12.57 (Enters first operand into the operand register, SR 3)

+(adds first operand to zero, already in the accumulator register, SR 1, SR 2.)

3874,06 (Enters second operand into the operand register, SR 3).

+(Adds first and second operands and stores answer in the accumulator register).

P (Prints answer on tape 14).

#### Subtraction

C, Clear.

89307.1 (Enters first operand into the operand register)

+(Adds first operand to zero, already in the accumulator register).

300.0 (Enters second operand into the operand register)

-(Subtracts second operand from the first operand 40 tor. and stores answer in the accumulator).

P (Prints answer on tape 14).

#### Multiplication

C, Clear.

387.684(Enters multiplier in the operand register).

+(Adds multiplier to zero, already in the accumulator register).

9.04152(Enters a multiplicand in the operand register).

X(Multiplies multiplier and multiplicand, prints answer on tape, and clears machine).

#### Division

3505.25(Enters dividend in the operand register).

+(Adds dividend to zero, already in the accumulator register).

387.684(Enters divisor into the operand register).

÷(Divides dividend by divisor, prints answer on tape, and clears machine).

FIG. 36 illustrates the resulting printout tape 14 format for the given key depressions of the above examples of addition, subtraction, multiplication and division

B lock diagrams of the principal components of the control and arithmetic sections of the calculator are illustrated in FIGS. 26–28.

All operations of the calculator, with the exception of the decimal point insertion in response to the decimal point key being depressed, employ the central control system of FIG. 26, which provides the timing clock and timing signals for the operations of the calculator. Referring to FIG. 26, the oscillator 311 comprising the gates identified within the block 311 of FIG. 18 in conjunction with the capacitor C 6 of FIG. 11 is activated whenever the calculator is turned on by switch 5. The oscillator 311 generates a 50 kilocycle per second output signal, which is applied to the gate 205, along with the command signals SA, PS, and SS. When the command signals PS, SA, and SS are all high, or in the one state, the oscillator 311 output is transmitted to the clock flip flop 302, comprising the group of gates within the block 302 of FIG. 18. The clock flip flop 302 generates square wave pulses CL and their compliment CL which define the timing signals used extensively throughout the calculator. The command signals, SA, 20 PS, and SS are generated by the internal circuitry of the calculator.

The S scale 312 comprising the group of gates within the block 312 of FIG. 18 is a 16-position counter and counts the clock pulses CL. The S scale is capable only of counting sequentially from one to 16, and the operations of the calcultor are timed by the 16 counts of the S scale. The four bit codes defining the 16 states, S 1 through S 16, of the S scale 312 are designated T 1, T 1, T 2,  $\overline{T}$  2, T 3,  $\overline{T}$  3, T 4, and  $\overline{T}$  4, illustrated in FIG. 18, in the manner that the position S 16, for example, of the S scale is  $\overline{T}$  4,  $\overline{T}$  3,  $\overline{T}$  2,  $\overline{T}$  1.  $\overline{T}$  1 is the least significant bit. Position S 16 is the normal position of the S scale. The 8 signals T 1, ... T 4 are connected to the decode gates 313 comprising the group of gates within block 313 of FIG. 18 which use the clock pulse complement CL from the clock flip flop 302, and the counting sequence of the S scale 312 to generate the timing signals to control the various nonreiterative operations (digit entry, add, subtract, clear, error) of the calcula-

For example, when the add key is depressed, the SS command is disturbed and caused to go high, allowing a single rotation of the S scale. Return of the S scale to its normal position S 16 regenerates the SS command, which blocks the gate 205 and stops the clock flip flop 302. Operations that require a single rotation of the S-scale are add, subtract, clear, error, and digit entry. The depression of any key except the decimal point key causes the clock flip flop to run.